许多工业和汽车应用中都使用了同步降压转换器电源拓扑结构;此类应用还要求具有低传导放射和辐射放射特性,以确保电源不会干扰共用同一条总线的其它设备(输入电压 [VIN])。例如,在汽车信息娱乐系统中,电子干扰(EMI) 会在汽车立体音响中发出挠人的噪音。

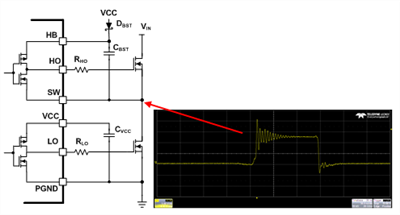

图1显示了同步降压转换器的原理图以及其开关节点波形。高侧MOSFET的开关速度和高侧/低侧MOSFET与印刷电路板(PCB)杂散电感和电容都具有在开关节点波形达到峰值时振铃的功能。而我们不需要开关节点波形振铃,因为它会增大低侧MOSFET的电压应力,并产生电磁干扰。

图1:同步降压转换器

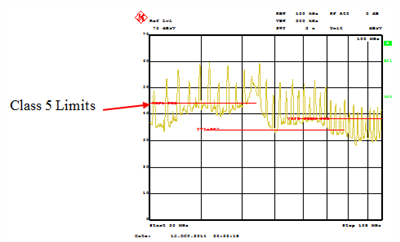

为了确定图1中降压转换器的开关节点振铃与其所产生电磁干扰之间的关系,我按照国家无线电干扰特别委员会(CISPR) 25 Class 5的规定进行了传导放射测试。图2显示了测试的结果。测得的数据显示:在30MHz-108MHz的频率范围内,降压转换器的传导放射值比Class 5限制高出了15dBµV。

图2:CISPR 25 Class 5, 30MHz-108MHz,降压转换器 VIN = 12V, VOUT = 3.3V, IOUT= 5A

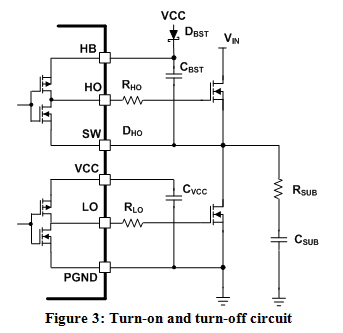

要降低电磁辐射,首先要降低开关节点的振铃噪声。有以下几种方法:首先减缓MOSFET的接通和关闭时间,从而控制开关节点的上升和下降时间。在串联电阻器(RHO与RLO)上加装MOSFET的栅极引线即可实现该功能;参见图3。第二步是在开关节点与接地之间加装一个缓冲器(RSUB与CSUB)。缓冲器电路可以在转换过渡期间抑制寄生电感和电容。

图3:接通和关闭电路

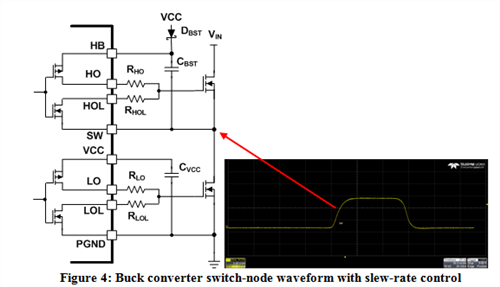

除利用上述方法来降低开关节点振铃噪音外,还有另一种方法,就是使用LM5140-Q1符合汽车应用要求的同步降压控制器。LM5140-Q1的一大重要特性是转换速率控制。通过引出驱动器的源侧和接收侧引线,可以独立控制高/低侧MOSFET的接通和关闭时间。

在低侧MOSFET关闭和高侧顶部MOSFET接通期间,开关节点电压从接地升至VIN。如果高侧顶部MOSFET接通过快,则在过渡时开关节点电压会过冲。增大RHO电阻可以降低高侧MOSFET的驱动电流,减缓该MOSFET的接通时间,同时有助于降低开关节点振铃噪音。注意:减慢高侧MOSFET的关闭时间会增大开关损耗。在低电磁辐射和高侧MOSFET的开关损耗之间选用RHO时,需要做一个权衡折衷。

低侧MOSFET损耗包括RDS(ON)损耗、空载时间损耗和MOSFET内部体二极管的损耗。空载(高/低侧MOSFET均处于关闭状态)时,低侧MOSFET的内部体二极管可传导感应器电流。一般情况下,MOSFET的内部体二极管都有较高的正向电压降,因此其效率会大幅降低。而缩短低侧MOSFET内部体二极管传导电流的时间可以提高效率。

利用转换速率控制可以在LM5140-Q1驱动器输出(LO引脚)和低侧MOSFET栅极之间插入一个电阻器(ROL),用来延长低侧MOSFET关闭所需的时间。减慢关闭时间可以减少低侧和高侧MOSFET传导的空载时间,提高降压转换器的效率。缩短同步降压的空载时间时,切勿同时传导高侧和低侧MOSFET。

图4:降压转换器开关节点波形和转换速率控制

我使用LM5140-Q1控制器(参见图4)改装了图1所示的电源。使用转换速率控制优化开关节点的上升和下降时间,消除了开关节点的振铃噪音。

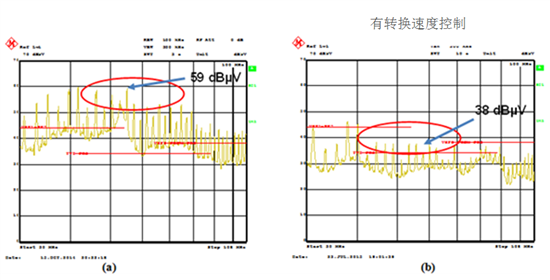

下一步是进行CISPR 25 Class 5传导放射。我选用了以下转换速率控制电阻器值:RHO = 10Ω, RHOL = 0Ω, RLO = 10Ω 和 RLOL = 10Ω。选择用于此应用的电阻器对于输入功率低于50W的任何应用来说都是一个很好的起点。

图5显示了传导放射测试的结果和总结。

图5:转换速率控制比较:CISPR 25 Class 5, VIN = 12V, VOUT = 3.3V, IOUT = 5A,无转换速率控制(a)和有转换速率控制(b)

降压转换器借助LM5140-Q1和转换速率控制将传导放射降低了21dBµV。此外还增强了对开关节点上升和下降的控制,同时无需使用缓冲电路,降低了电路的复杂性和成本。

挑选出转换速率控制电阻器的正确值,不仅可以降低电磁辐射,还能同时提高系统的效率。

请参加3月21-23日在加州长滩举行的国际电力电子应用会议(APEC)莅临德州仪器展台(1617号展台),观赏LM5140-Q1降压转换器的现场演示。登录www.ti.com/apec2016了解德州仪器的相关信息。

其它资源

观看“Engineer it:如何使用转换速率控制降低电磁辐射”。

参见LM5140-Q1数据表。

打开“LM5140-Q1评估模块用户指南。”

原文链接:

https://e2e.ti.com/blogs_/b/powerhouse/archive/2016/03/21/how-to-use-slew-rate-for-emi-control