作者:Frank Qin

问题背景:

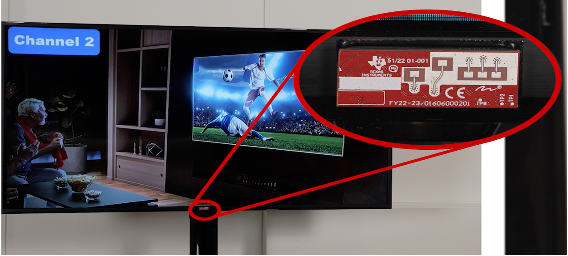

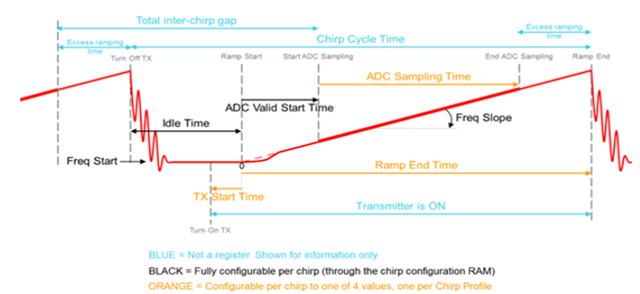

在IVI系统中,SoC-串行器-解串器-屏幕的链路中存在很多的干扰及未知因素。尤其是当下各类芯片基本都没有提供各类信号的并行输出,导致难以在串行链路中的各个点位分别抓取我们希望得到的数字信号,从而导致在整个系统出现不稳定或者时钟及脉冲信号不匹配时,我们无从下手去找到不匹配的点。

解决思路:

如果可以把串行信号或者“黑盒子”中的有意义的信号单独抓取出来,找到其中的“可变量”和“定量”,就可以比较简单的判断出链路中是否有哪个信号出现的偏差或抖动。

LVDS 可在并行和串行数据传输中工作。 在并行传输中,多个数据差分对同时承载多个信号,其中包括用于同步数据的时钟信号。 在串行通信中,多个单端信号被串行化为单个差分对…

模拟

模拟 汽车

汽车 DLP® 技术

DLP® 技术 嵌入式处理

嵌入式处理 工业

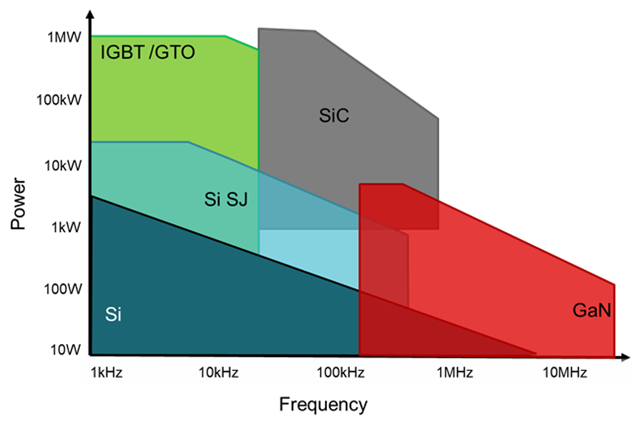

工业 电源管理

电源管理