TI的SAR-ADC方面资深应用工程师Rafael曾说过,SAR-ADC应用电路设计重点的70%-80%应放在基准源电路的设计。然而工程师们时常把基准源的电路的设计忽略。

这个问题常常被忽略的原因可能来源于我们大学期间的教材。众多《数子电路基础》教材中,一般都没有给出SAR-ADC内部的电容网络结构,《模拟电路基础》教材也很少讨论基准源。然而在SAR-ADC设计时基准源的电路设计是至关重要的。简单理解,基准都不精确、干净、稳定,就不用指望转化出来的结果会精确。下面从ADC的内部结构和基准电路的设计要点,来说明基准源设计的重要性,并给出支持16bits SAR-ADC的基准电路设计。

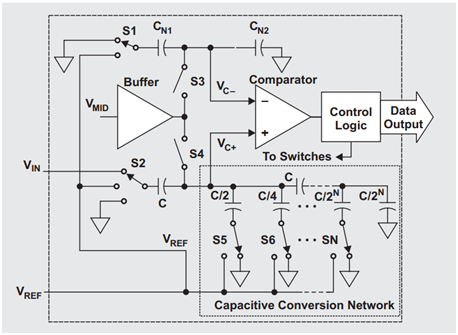

下图是SAR型ADC的内部原理简图,SAR-ADC在采样过程中输入引脚AIN要对内部的采样电容充电。而转化过程中,Vref基准源引脚要对转化电容网充电。简而言之SAR-ADC的采样保持和量化过程,都是有对内部电容的充电过程。读过相关文章“Design SAR-ADC Driver Cirtuitry”工程师,都会深刻理解SAR-ADC驱动电路后,ADC输入引脚电容的重要性。原因是在采样保持过程中SAR-ADC采样电容会从输入引脚AIN驱动电容上抽取电荷。

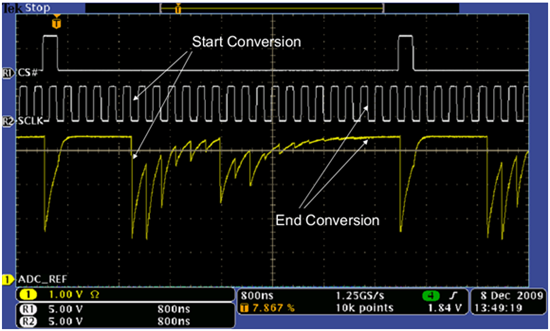

常被忽略的地方是,整个采样转化周期里,SAR-ADC需要从信号电路中抽取一次电荷,而要从基准源REF中抽取N次电荷(N等于ADC的位数),而且抽取的周期更短(一个转化时钟的周期)。这就要求基准源在整个转化过程中,能够更快的给转化网络电容充电,并且保持基准源的恒定。确切的说比信号驱动电路的要求更高。下图是一个基准源设计不良时,转化过程中的基准源引脚电压,由示波器测得。由图可知,每个转化时钟周期,ADC都要从基准源上抽取电荷,并且要求恢复时间极短。

看了上图中基准源引脚上的电压在采样过程中的变化,我们会深刻的理解到SAR-ADC的基准源引脚稳定的重要性。我们总不希望在SAR-ADC转化的MSB位时,基准电压是2.500V,到LSB位时,就变成了2.498V。

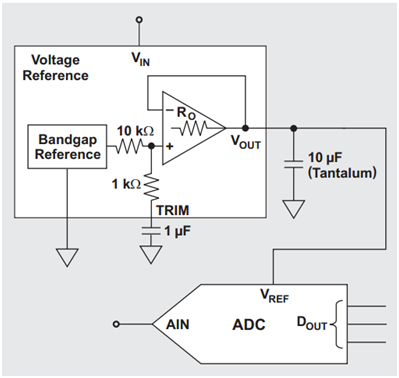

下图一个典型的基准源连接ADC的电路。这个电路适合于给8-14倍的ADC提供基准。我们多数情况下,会关注基准源的初始精度,但这个精度是可以通过软件或硬件调整的。SAR-ADC的基准电路设计有很多更值得关注的地方。如引脚电容,这个电容是给内部的转化网络提供电荷,至关重要,但常被忽略。

在下面的小节里,会一步一步的解释基准源电路的设计要点,尽量说清楚两个问题,(1)为什么要这样设计,(2)怎样进行基准源电路设计。为了增强说服力,增加了文献中的效果对比,有数据有图表,希望对大家有用。