请教 Martin:

在LMP91300的数据手册里有以下这段:

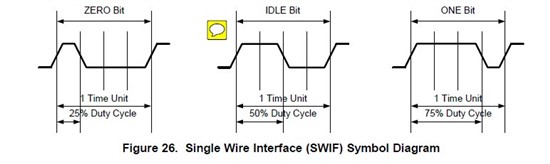

Single-Wire Interface (SWIF)

The LMP91300 uses a bi-directional Single Wire Interface protocol to program and read registers. To

communicate with the LMP91300 (slave) through the SWIF interface, the micro controller (master) must transmit

(write) data through the DC loop supply voltage that should be set to +8V during programming or communication.

This superimposed signal of pulses transitions between 8V and 12V is on top of the +8V DC loop supply voltage.

When the master transmits data into the LMP91300 the signal propagates into the SENSE2+ pin through the

supply. The master receives data from the LMP91300 through the LED pin in the form of alternating current

pulses. These current pulses will be 5mA in amplitude. The LED pin must be connected to ground, either through

an LED or directly connected to ground for the LMP91300 to talk to the master.

能详细解释一下吗?

我已按下面图做出好编程器.但不明白供电电压8V和12V分别在何时提供?

请求指点.