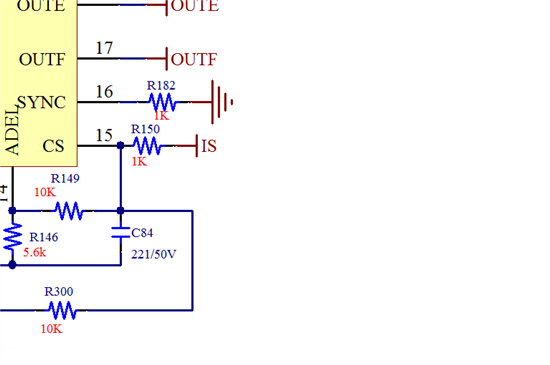

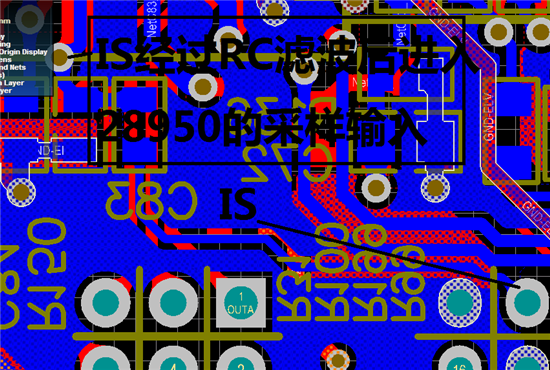

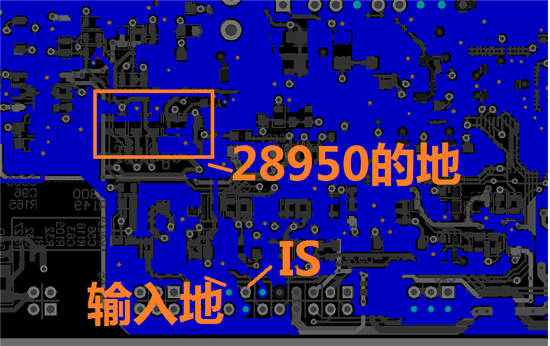

我正在进行UCC28950的3KW DC-DC的样件调试,遇到一些问题,需请教下TI的FAE ,

首先介绍下,工作条件:input 400-700V 输出 27V/110A;

我现在遇到问题是: 不加不同整流情况下, 加载到12A ,输出稳定,驱动稳定,但此时已移相到最大

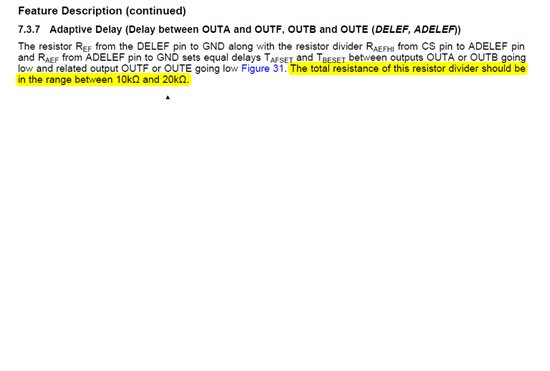

占空比( 540V输入条件下), 再往上加载,COMP脚电压不变,驱动开始不稳抖动,是不是我的反馈环路有

问题,从0-12A的加载条件下 ,COMP上升,移相持续加大,未出现驱动不稳的情况 ,

现在持续加到30A,芯片保护,开始ss脚 打嗝重启了。请帮忙看下是什么问题导致的 。

此问题困扰我一个星期了,通过调整电压反馈参数未有根本改变,还希望高手能指导下!不甚感激

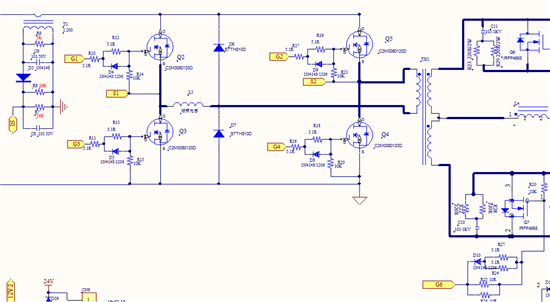

我的设计

变压器匝比:24:2 , PQ50

输 出电感: 2.0uH,

开关频率:100KHz

目前谐振电感: 6uH

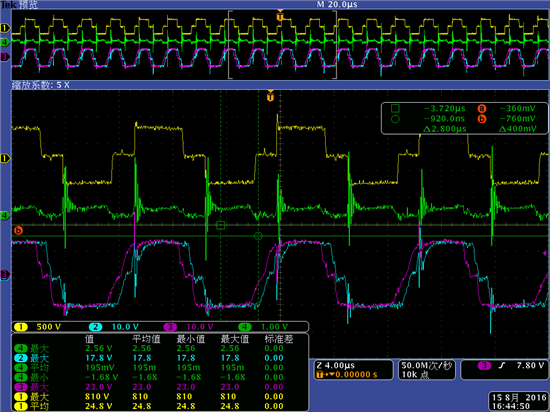

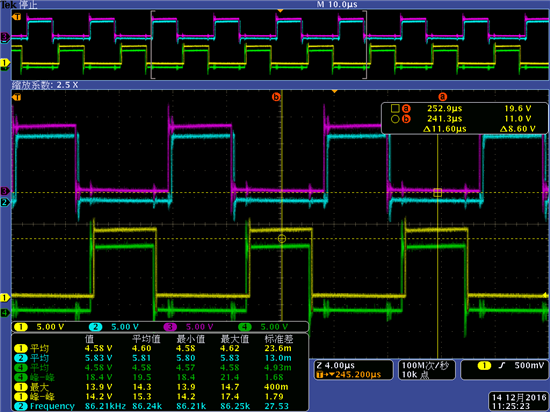

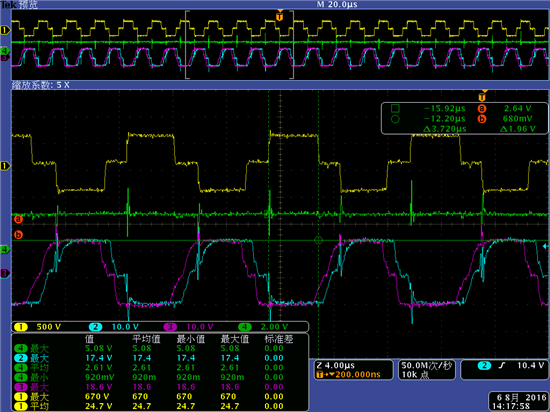

附件的为30A负载下 波形

CH2,CH3分别是 OutA OutD的Vgs, CH1: 变压器原边Vtx , CH4: COMP 脚电压

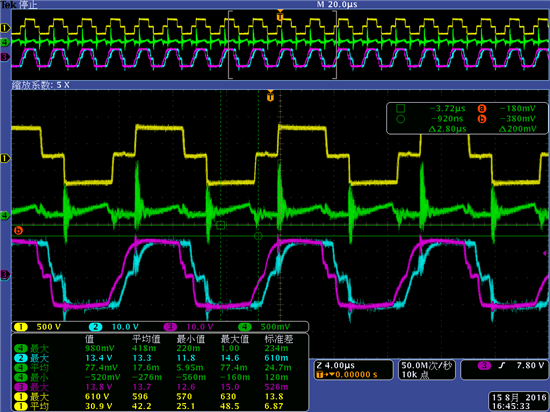

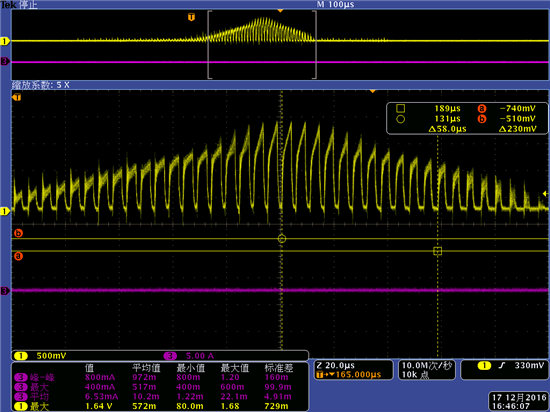

如下是30A 负载下波形

其中 CH4为 CS脚波形

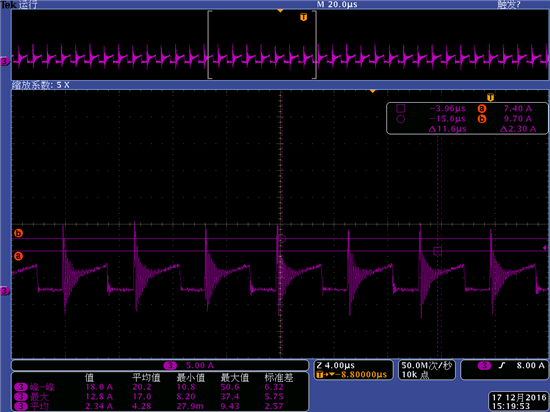

如下为 12A 负载下波形