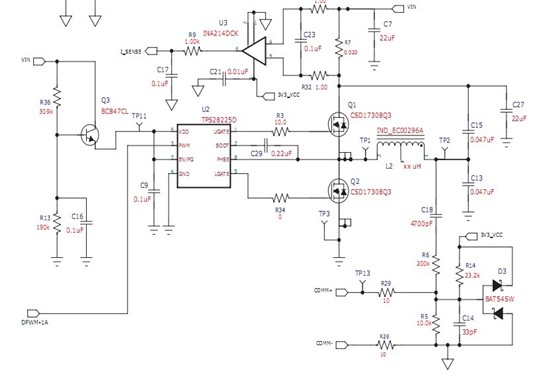

驱动芯片TPS28225的3脚PWM输入PWM波形,测得输出波形,CH1:PWM波,CH3:Ugate,CH4:Lgate。UGATE高电平时的电压值24V左右,Lgate的高电平时的电压值6.7V左右。这两个门电压值跟什么因素有关,是如何得出的?为什么不一样?请专家指导一下,谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

驱动芯片TPS28225的3脚PWM输入PWM波形,测得输出波形,CH1:PWM波,CH3:Ugate,CH4:Lgate。UGATE高电平时的电压值24V左右,Lgate的高电平时的电压值6.7V左右。这两个门电压值跟什么因素有关,是如何得出的?为什么不一样?请专家指导一下,谢谢。

你好。请问下UGATE电压为什么是24V而不是其他的?TPS28225的管脚UGATE与LGATE参数中有源电流source current与灌电流sink current,这两个参数如何理解?能具体说明 一下吗?

你好。请问下UGATE电压为什么是24V而不是其他的?TPS28225的管脚UGATE与LGATE参数中有源电流source current与灌电流sink current,这两个参数如何理解?能具体说明 一下吗?

不好意思,我又仔细看了一下28225的PDF文档,前面的描述有问题,正常情况下,高端驱动应该比VDD电压略低一些才对(受二极管影响),你能提供你的原理图看看吗?至于Source电流指该点输出电流的能力,Sink电流指灌电流能力,通俗的说就是图腾柱的驱动能力。

能测量一下PHSE端对地的波形与BOOST端对地的波形来看看吗?

你好!测量的28225的boot与phse的波形如图:通道1:boot,通道3:phse

问个问题,你测UGATE点波形的时候,是不是不是以Phse点为参考测的而是以输入地为参考测量的?

呵呵,当然有问题,当上管有驱动信号的时候,下管已经关闭,此时Ugate点电压是在PHSE点电平的基础上叠加有一个VDD电压。而此时PHSE点电压是输入电压,那么Ugate点电压就变成了输入电压+VDD点电压-二极管压降。

哦,这样理解了,谢谢你哈。上管的驱动电压就是相对与phse管脚的电压就是VDD-内部二极管的压降的值了。

对了,你是否了解半桥电路,就是原理图中Q2,Q3,C23,C27,构成半桥电路。Q2导通时,电流方向:Q2,电感,C27,对电容C27充电;Q3导通的时候,电流的方向:C23,电感,Q3。有一点不太明白,电容是隔直流,当Q3导通的时候,VDD19电流如何流过C23,电感,Q3。感觉是C27放电,流经电感,Q3。C23电容没有什么用。请指教一下,谢谢!

我说我没看明白你这个图到底是什么拓扑。

先不管这个图是否正确,来解答一下你的问题:由于C23、C27是串联后接在输入端的,因此两个电容上电压之和是不变的,按照你的理解,当Q3导通的时候,流过Q3的电流是由电容C23、C27共同提供的。也就是C23充电、C27放电。你说的C27放电是对的,但C27放电电压必然降低,而C23与C27电压之和保持不变,C23就是充电,也就是电流方向C23是从上到下,C27是从下到上。不知道这样说是否明白?

你好,下图是正确的mos驱动电路,和我上面提供的一样。当Q2导通时,C13放电,电流由下到上,这个明白。当C15充电,电流由上到下,这个就不太明白了。

若Q1导通时,电流流经Q1,电感,C13,对电容C13充电,此C15放电。Q1的电流由C15,VIN提供是这样的吗?请指教,谢谢。

这样说吧,如果Q1导通,输入电流为I,那么输入电流通过Q1,电感、给C13充电,由于C13与C15上的电压之和保持不变,必然有一个同样的电流给C15放电,C13充电电流是从上到下,C15的放电电流是从下到上,C15放电路径为C15、Q1、电感。这样流过电感(一般是变压器原边)的电流就是2I,由于变压器原边承受电压正好是输入电压一半,电流两倍正好是传递输入功率。

C13放电,电流由下到上,这个明白。当C15充电,电流由上到下,这个就不太明白了。。。。这个也好理解吧,两个电容串联,然后与输入电压并联在一起,一个充电另一个必然放电,否则两个电容电压如何保持不变?

你好,关于这个电路半桥电容值的计算,是如何计算的?跟什么参数有关?能详细讲解一下吗?谢谢!