在TI官方给出的电源套件-TIDM-1001 LLC的PWM_HB_LLC_2PHIL_SR.c里面有关于互补PWM的初始化程序,我感觉有问题,向大家请教下,请不吝指教。

我只留下关键代码,其他的一些初始化代码略去

void PWM_HB_LLC_2PHIL_SR(int16 n, int16 m, int16 period)//这里用的是EPWM1A和1B,所以n=1

{

(*ePWM[n]).TBPRD = period/2;

(*ePWM[n]).TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;

// Counter Compare Submodule Registers

(*ePWM[n]).CMPA.bit.CMPA = 1; // Start with 50% duty (Avoid using CMP = 0)

(*ePWM[n]).CMPB.bit.CMPB = period/2 - 1; // Start with 50% duty (Avoid using CMP = PRD)

// Action Qualifier SubModule Registers//以下三行设定的是EPWM1A 50%占空比输出,没什么问题

(*ePWM[n]).AQCTLA.bit.ZRO = AQ_CLEAR;

(*ePWM[n]).AQCTLA.bit.CAU = AQ_SET;

(*ePWM[n]).AQCTLA.bit.PRD = AQ_CLEAR;

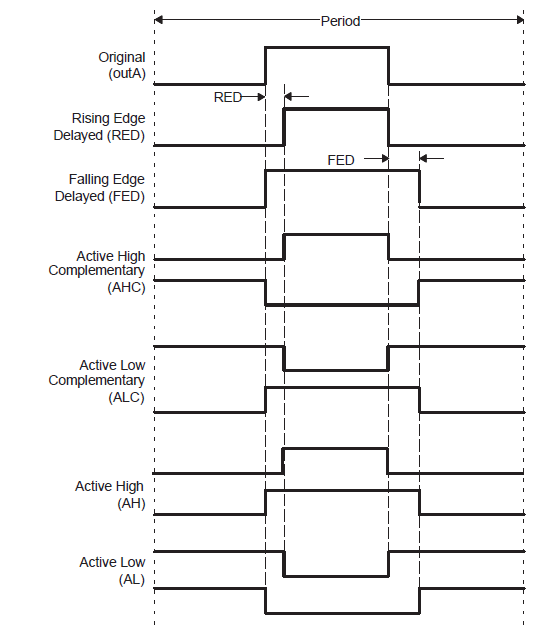

// xB AQ output is inverted by DB for RED on xB output//以下三行设定的是EPWM1B 50%占空比输出,我的问题就在这儿,感觉1B和1A同相位,而不是相位互补

(*ePWM[n]).AQCTLB.bit.PRD = AQ_SET;

(*ePWM[n]).AQCTLB.bit.CBD = AQ_CLEAR;

(*ePWM[n]).AQCTLB.bit.ZRO = AQ_SET;

}

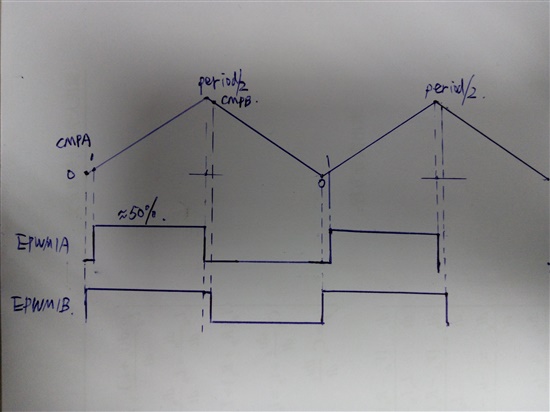

按照代码里的Action Qualifier设置,我觉得波形应该如下图所示

这里是不是有什么问题,或者是我的理解错了