TI工程师:

您好!最近看了《Three-Phase High PWM Frequency GaN Inverter Reference Design TIDA-00915》参考设计。对里面的高速电路有一些细节不理解,请指点。

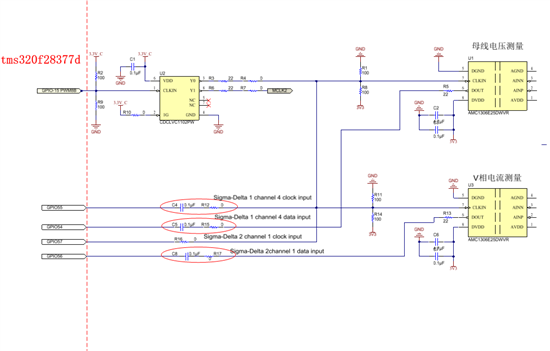

电路信号链路如下图所示。tms320f28377d的PWM作为时钟信号通过 buffer(CDCLVC1102PW)为4片Sigma-Delta ADC转换器(图中只画了2片)提供时钟信号。设计者考虑阻抗匹配,并联两个100欧姆和串联22欧姆电阻实现阻抗匹配。但为什么会串入0.1uF的电容呢?

具体问题如下:

1、将Sigma-Delta ADC输出信号串入0.1uF电容,再进入DSP管脚,是阻抗匹配的需要吗?串入容值的大小计算,您能推荐文档吗?

2、设计者也不是所有都串入了0.1uF电容,直流母线电压测量的clk,就没有串入。是漏掉了,还是其它原因呢?

3、设计者多处串入0欧姆电阻,是调试需要,(因为28377的Sigma-Delta ADC模式2 可以不需要时钟信号),还是有其它讲究?

4、关于何时需要考虑阻抗匹配?一些文档说,对于20MHz信号,PCB走线超过50mm,就需要考虑。另一文献说信号上升沿和下降沿小于6倍信号延时就需要考虑。您对何时需要考虑,有什么建议吗?因为TI参考电路《使用 SAR 和 Σ-Δ ADC 在保护继电器中实现集成诊断功能的参考设计 TIDA-00810》同样的电路,就没有考虑阻抗匹配。