我用两块28035做SPI通信,一个是主机一个是从机,主机发送的数据没什么问题,但从机在接收一段时间后开始出现数据错位

下面是主从机初始化的函数

if(DeviceType == MasterDevice)

{

SpibRegs.SPIFFTX.all = 0xe000; // 不产生中断,主循环中轮询

SpibRegs.SPIFFRX.all = 0x0024;

SpibRegs.SPIFFCT.all = 0x0000;

SpibRegs.***.all = 0x000f;

SpibRegs.***.all = 0x000e;

SpibRegs.SPIBRR = 59; //15m/30

SpibRegs.***.all =0x008f;

SpibRegs.SPIFFTX.bit.TXFIFO = 1;

SpibRegs.SPIFFRX.bit.RXFIFORESET=1;

GpioDataRegs.GPACLEAR.bit.GPIO15 = 1;

}

else

{

SpibRegs.***.bit.SPISWRESET=0; // Reset SPI

SpibRegs.***.all=0x000F; //16-bit character

SpibRegs.SPIBRR = 59; //15m/15

SpibRegs.SPIFFTX.all = 0xc001; //

SpibRegs.SPIFFRX.all = 0x0024;

SpibRegs.SPIFFCT.all = 0x0000;

SpibRegs.***.all = 0x000a;

SpibRegs.***.bit.SPISWRESET=1; // Enable SPI

SpibRegs.SPIFFTX.bit.TXFIFO=1;

SpibRegs.SPIFFRX.bit.RXFIFORESET=1;

}

这里我有几个疑问

首先,在时序模式的四种配置中,我选择了CLK_POLARITY = 0;CLK_PHASE = 1;这时候SPI在SPICLK信号第一个上升沿之前的半个周期开始输出数据,在SPICLK信号的上升沿将输入的数据锁存。 这里我有个疑问,我的片选信号一直是拉低的,从机怎么在SPICLK信号第一个上升沿之前半个周期就开始输出数据呢?换句话说,从机只有检测到第一个SPICLK上升沿才知道主机在传输数据,那它怎么会提前半个周期输出数据到SPISOMI呢,未卜先知?。。

第二个问题,在传输数据出现错位后如何清除接收缓冲寄存器和发送缓冲寄存器?我这里用了FIFO缓冲寄存器,对于这个先进先出的寄存器,我总感觉这里的数据没有完全清掉导致的数据错位?

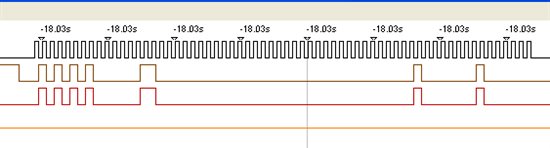

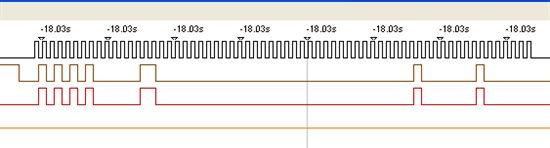

正常的数据

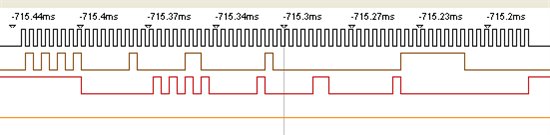

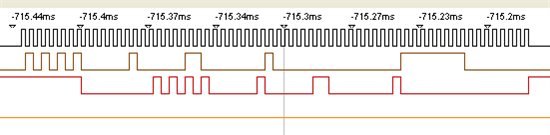

错位的数据