设计的CC2350 Module的EVM(Error Vetor Magnitude)值偏大,多个样本测试值基本都在39%,高于规范的要求(低于30%),请问如何降低EVM值?

注1:原理图直接参考官方的CC2530EM设计,器件参数取值也是一致的,只是品牌不一致,不过晶振频偏为17ppm左右。

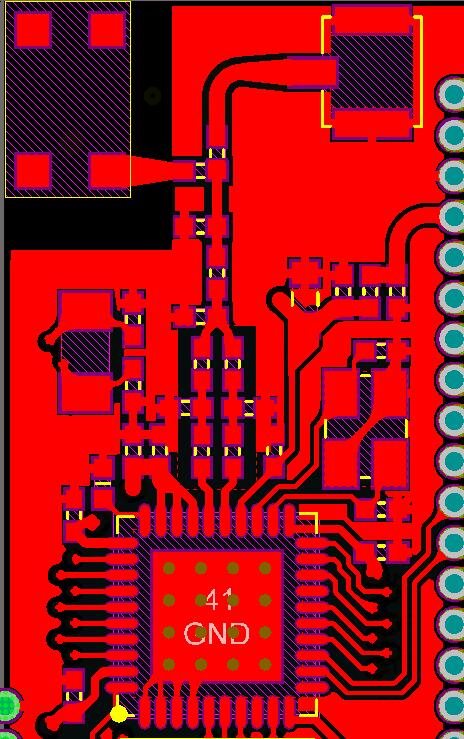

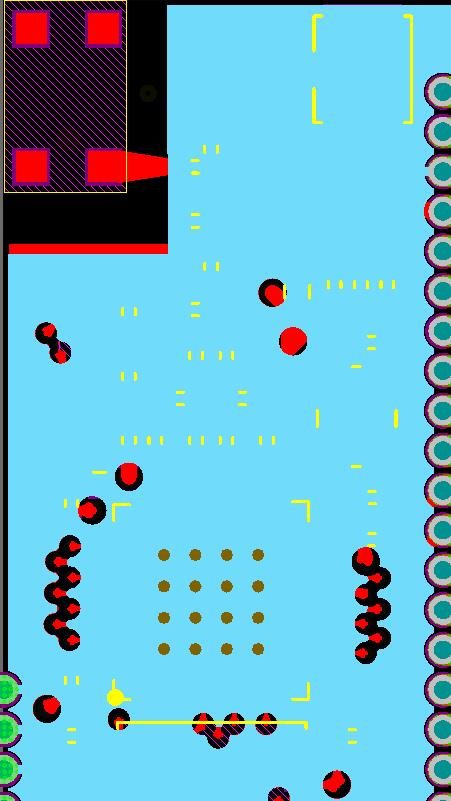

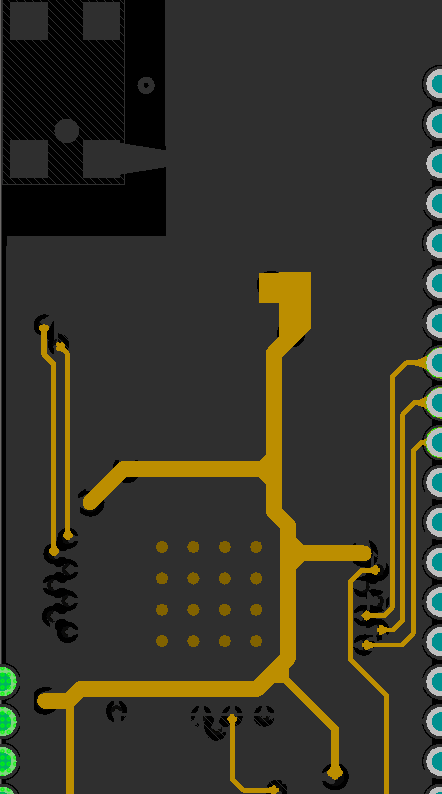

注2:Layout也是根据射频电路设计要求,结合实际板子大小设计,设计图如下。包括射频线路的50Ω阻抗要求、旁路电容要求,走线要求都有考虑,不知哪些没考虑到?

目前产品就卡在EVM值过不了的问题, 希望能尽快帮忙指出不足之处,谢谢!