void InitEPwm2Driver(void)

{

EALLOW;

EPwm2Regs.TBPRD = C_MOTOR_PWM_PRD;

EPwm2Regs.TBPHS.all = 0;

EPwm2Regs.TBCTR = 0;

// Setup TBCLK

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;

EPwm2Regs.TBCTL.bit.PHSEN = TB_DISABLE;

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm2Regs.TBCTL.bit.SWFSYNC = 0;

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.PHSDIR = 1;

EPwm2Regs.TBCTL.bit.FREE_SOFT = 3;

EPwm2Regs.CMPA.half.CMPA = 1125

//EPwm2Regs.CMPA.half.CMPAHR = 0;

EPwm2Regs.CMPB = 1;

//EPwm2Regs.CMPA.half.CMPAHR = 0;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm2Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm2Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CBU = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CBD = AQ_SET;

EDIS;

}

PWM模块配置如上,其中B路PWM在其正常工作的时候,将CMPB值更新为0,停止PWMB的输出。

经过验证,如果更新CMPB值的时刻,正好为时基计数器为0的时刻,此时会出现PWM2B被异常拉高一个周期。

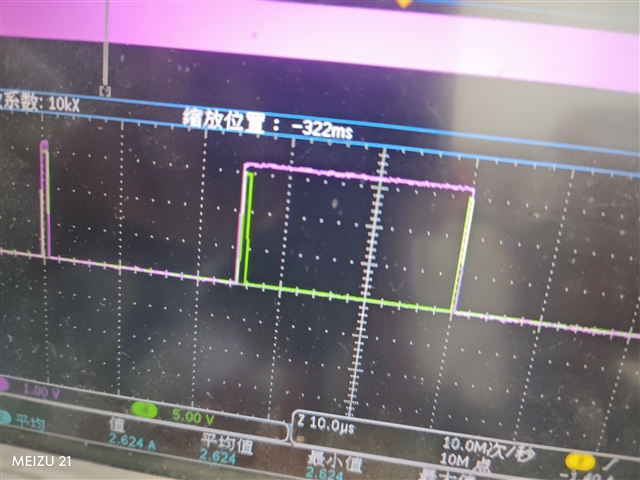

如上图所示,紫色波形为出现问题的EPWM2B输出波形,绿色波形为EPWM3B的波形,其配置与EPWM2B相同,且占空比更为位置也相同,理论上这两者波形应该一致。

左侧紫色和绿色的小尖峰是出问题前一时刻,正常的PWM输出的波形,占空比为3.2%,在后一个PWM周期,软件给PWM2B 和3B的CMPB同时给到0,输出0占空比,从而不输出波形,但是此时2B输出出现问题,波形被异常拉高一整个周期,绿色的仍为正常波形。

后续经验证了十几次,发现紫色的EPWM2B波形出问题的时刻,总是在时基计数器数到0时刻,给CMPB写0停止输出这个时间节点。

因为配置的是比较值影子寄存器在CTR=0时刻进行装载,不知道和应用层刚好在CTR=0时刻把CMPB写为0是否有关。